GaN and SiC Devices and Modules

D04.10 - GaN Power Module Design with Fully Integrated Gate Driver to Achieve Beyond 200 V/ns Switching Speed

Thursday, March 26, 2026

12:00 PM - 1:45 PM CT

Location: Hemisfair Ballroom

- RS

Reza Shahbazi (he/him/his)

The Pennsylvania State University

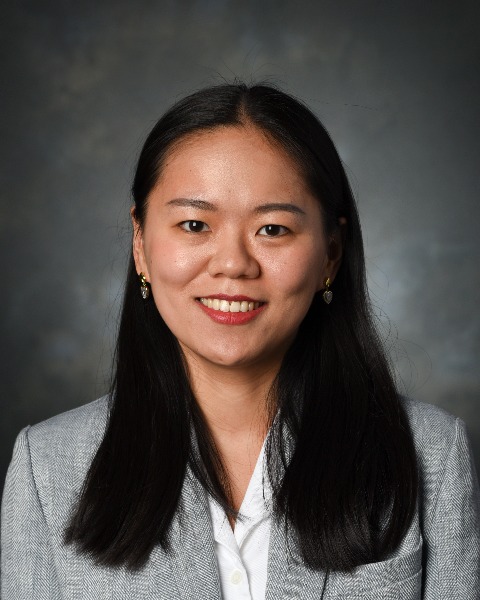

Yunting Liu, PhD

Penn State

Technical Dialogue Presenter(s)

Co-Author(s)

Gallium nitride (GaN) switches enable extremely fast switching speeds, making them ideal for high-power-density systems. However, their performance is often restricted by sensitivity to layout parasitics. Even with recent advances in PCB and module design, many implementations still exhibit suboptimal power and gate loop inductances. These non-ideal parameters can increase turn-off voltage overshoot and cap the achievable switching speed (dV/dt) at below 200 V/ns. This paper introduces a double-sided cooling 650 V/60 A GaN half-bridge power module with the dimensions of 23 mm × 21 mm featuring an integrated gate driver and optimized parasitic parameters. The paper presents the structural layout, as well as the power loop and gate driver design based on their damping factor ratio to achieve the damping factors of 1. The ANSYS Q3D extractor measures the power loop inductance of 0.60 nH and gate loop inductance of 0.29 nH. These values were incorporated into a SPICE-based simulation model. Experimental validation of the prototype confirms a maximum drain–source voltage VDS slew rate of 208.3 V/ns with the overshoot limited to only 6%.