GaN and SiC Devices and Modules

D25.1 - A Master-Slave Gate Driver Architecture for Paralleling of Medium-Voltage SiC MOSFET Power Module with Oscillation Feedback Path Blocking

Thursday, March 26, 2026

12:00 PM - 1:45 PM CT

Location: Hemisfair Ballroom

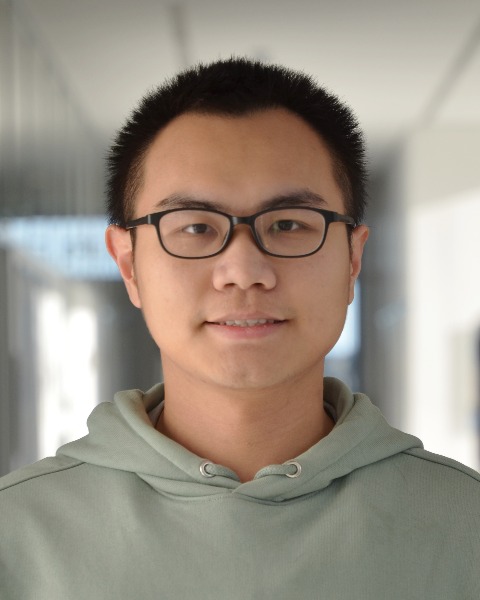

Gao Liu

Aalborg University

Zhixing Yan

Aalborg University

Hongbo Zhao

AAU Energy

- SM

Stig Munk-Nielsen

Aalborg University

Technical Dialogue Presenter(s)

Co-Author(s)

Gate oscillations in paralleled SiC MOSFET power modules occur during switching transients, potentially causing false switching behavior and device damage. In our previous work, mitigation strategies by adjusting parasitic inductances were proposed. However, as the number of paralleled modules increases, mechanical design constraints limit the effectiveness of optimizing parasitic distribution. To overcome this a master-slave gate driver architecture that simplifies the gate-driver circuit for multiple paralleled modules is introduced in this paper. Blocking inductors and damping resistors are incorporated into the slave driver board to suppress oscillation feedback paths. Experiments on a double pulse test platform with three paralleled 10 kV modules confirm the architecture’s effectiveness.